DOI: 10.7500/AEPS20230706005

Automation of Electric Power Systems

# 双有源桥型电力电子变压器电磁暂态实时低耗等效模型

高晨祥1,林丹颖1,韩林洁2,冯谟可1,许建中1,李彬彬2

- (1. 新能源电力系统国家重点实验室(华北电力大学), 北京市 102206;

- 2. 哈尔滨工业大学电气工程及自动化学院,黑龙江省哈尔滨市 150001)

摘要:电力电子变压器(PET)是柔性直流配电网中电能变换的关键设备。受仿真资源限制,现有PET 电磁暂态(EMT)实时仿真规模较小,无法满足大容量系统硬件在环测试与快速仿真需求。文中提出一种双有源桥(DAB)型PET实时低耗等效建模算法。首先,深入挖掘了DAB高频链端口解耦模型的二值输入导纳特性,并从数值分析与物理意义两个层面进行了阐述。以此为基础,构建了具有N+1特性的PET高频链端口解耦模型。其次,提出了基于有限存储的低内存占用EMT解算方案、紧凑型低延时仿真框架、分组并行流水线计算硬件实现方案,降低了所提等效模型在实时仿真中对存储内存、计算时钟和硬件资源的需求。最后,在RT-LAB中完成了基于Verilog语言的250 ns实时低耗等效仿真模型开发,并进行了所建模型仿真精度和资源利用率测试。

关键词: 电磁暂态实时仿真; 电力电子变压器; 双有源桥; 高频链端口解耦; 低资源消耗; RT-LAB

# 0 引言

电力电子变压器(power electronic transformer, PET)因其安全稳定的电压变换、可靠灵活的功率控制等功能,在当前大规模交直流混联、新能源汇集的电力系统发展需求下,展现出十分重要的理论研究与工程实用价值<sup>[1-3]</sup>。使用高频链(high frequency link, HFL)隔离的双有源桥(dual active bridge, DAB)型PET是其中的关键设备之一<sup>[4]</sup>。

电磁暂态 (electromagnetic transient, EMT) 实时仿真具备效率高、可控制器硬件在环调试等诸多优势,已成为设备级效率、功率密度、经济性测试,以及电网级在线分析、故障预演等方面研究分析的重要工具<sup>[5-7]</sup>。随着 PET 在配电网中的应用,其实时仿真研究受到广泛关注。当前,PET 的电磁暂态实时仿真研究面临以下困难和挑战<sup>[8-11]</sup>:

1)高频链的工作频率日渐提高,为实现对高频瞬态过程的精确拟合,实时仿真过程中要求采用很小的仿真步长,常为最小开关周期的1/100~1/20<sup>[12-13]</sup>(1 μs 及以下)。这要求 PET 的实时仿真模型具有很好的并行性和低仿真延时。

收稿日期: 2023-07-06; 修回日期: 2023-11-06。

上网日期: 2024-02-23。

北京市自然科学基金面上项目(3222059)。

- 2) 模块结构复杂,模块间拓扑连接方式多样<sup>[14]</sup>,导致了很高的计算复杂度。但是,实时仿真硬件平台,如现场可编程门阵列(field-programmable gate array,FPGA)等,硬件资源有限,限制了仿真规模。

- 3)模块化级联的结构使得 PET 节点导纳矩阵的阶数很高,且开关器件多。网络解算过程中,面临大量的大规模矩阵存储,对内存要求较高。

目前,针对PET实时仿真的研究按开关器件的建模方法,可分为以下3类:

1)基于L/C定导纳开关模型的实时仿真。L/C模型具有节点导纳矩阵不随开关状态改变的优良特性<sup>[15-17]</sup>,被广泛应用于主流的商用实时仿真软件,如RTDS、RT-LAB。文献[18]基于RT-LAB的库元件和eHS解算器,搭建了包含3个DAB模块的800 ns PET实时仿真模型。为解决高频情况下L/C模型的虚拟功率损耗问题,文献[19-21]提出了基于响应匹配的广义L/C模型,实现了3个DAB模块的250 ns实时仿真及硬件在环测试。相比于基于常规L/C开关的实时模型,该模型在仿真精度方面得到极大提高。但是,其对仿真资源的需求相对较高,仿真规模问题尚未得到很好解决。

2)基于二值电阻开关模型的实时仿真。二值 电阻模型可准确反映电力电子装备的系统级特性,

被广泛应用于 PSCAD/EMTDC 等离线仿真软件中<sup>[22]</sup>,但是存在由开关状态切换引起的节点导纳矩阵时变问题。在实时仿真过程中通常引入矩阵预计算与存储过程来克服这一问题。文献[9]基于模态划分和节点导纳逆矩阵存储,实现了单个 LLC 谐振变换器 25 ns(5个时钟)实时仿真。文献[11]通过将矩阵存储与分层并行技术结合,实现了 42个 DAB模块实时仿真。但是,当开关数量和节点数量较多时,内存需求量将急剧增加,仍面临仿真规模受限问题。

3)基于理想开关函数的实时仿真。文献[23-24]通过对高频链单元的分析,将开关器件的导通关断表征为理想开关函数,进而交直流侧的相互影响可以由受控电压、电流源的形式体现。这种方法避免了L/C开关模型中的虚拟功率损耗问题和二值电阻开关模型的节点导纳矩阵时变问题,但是这种模型不能反映真实的换流单元器件损耗、压降等特征,并且受控源控制信号的产生和赋值会给电路部分带来一个时间步长的延时,影响仿真精度。

总体而言,当前PET实时仿真方法仍面临计算延时高、资源消耗多、内存占用大等方面的问题,为适应大容量模块级联场景的实时仿真需求,需进一步开展PET电磁暂态实时仿真算法研究。

本文借鉴文献[25]中"高频链端口解耦"的思路,提出一种DAB型PET实时低耗等效建模算法。首先,深入挖掘了DAB高频链端口解耦模型输入导纳的二值特性,给出了其数值和物理解释,构建了具有N+1特性的PET高频链端口解耦模型,为实时仿真提供算法支撑。其次,为降低对实时仿真内存、计算时钟、硬件资源3个方面的需求,利用DAB模块等值参数的二值特性,提出基于有限存储的低内存占用EMT解算方案;通过紧凑型计算逻辑,实现低延时实时仿真框架构建;利用等效算法的高度并行性,提出多模块分组并行的流水线结构。最后,基于Verilog语言,完成RT-LAB实时等效仿真模型的开发,通过与PSCAD/EMTDC中详细模型的对比,验证实时等效建模算法的精度,并进行了多模块资源利用率测试。

# 1 DAB型PET高频链端口解耦等效模型

#### 1.1 拓扑及工作原理

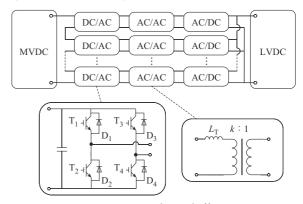

DAB型PET电路拓扑如图1所示,各模块采用输入串联输出并联(input series output parallel, ISOP)方式连接,其传输功率通过移相角控制<sup>[26]</sup>。图中:MVDC和LVDC分别表示中压直流和低压直

流;L<sub>T</sub>为变压器电感;k为变压器变比。

图 1 DAB型 PET 拓扑

Fig. 1 Topology of DAB-based PET

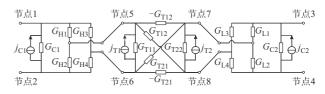

采用二值电阻模型对绝缘栅双极晶体管 (IGBT)/二极管开关组进行等值,采用后退欧拉法 离散电容、电感和变压器,所得 DAB 模块伴随电路 如图 2 所示。

图 2 DAB 模块伴随电路 Fig. 2 Companion circuit of DAB module

图 2 中的  $G_{\text{HI}} \sim G_{\text{H4}}$ 和  $G_{\text{LI}} \sim G_{\text{L4}}$ 为二值导纳值,其他部分参数表达式如式(1)所示[25]。

$$\begin{cases} G_{\text{C}i} = \frac{C_{i}}{\Delta t} & i = 1, 2 \\ j_{\text{C}i}(t) = G_{\text{C}i}v_{\text{C}i}(t - \Delta t) & i = 1, 2 \end{cases}$$

$$\begin{cases} G_{\text{T}} = \begin{bmatrix} G_{\text{T}11} & G_{\text{T}12} \\ G_{\text{T}21} & G_{\text{T}22} \end{bmatrix} = \Delta t \begin{bmatrix} L_{\text{T}} + L_{1} + L_{\text{m}} & \frac{L_{\text{m}}}{k} \\ \frac{L_{\text{m}}}{k} & L_{2} + \frac{L_{\text{m}}}{k^{2}} \end{bmatrix}^{-1} \\ j_{\text{T}i}(t) = -i_{\text{T}i}(t - \Delta t) & i = 1, 2 \end{cases}$$

$$(1)$$

式中: $L_1$ 、 $L_2$ 和 $L_m$ 为变压器电感参数; $\Delta t$ 为仿真步长; $G_{Ci}$ 、 $j_{Ci}$ 和 $G_T$ 、 $j_{Ti}$ 分别为电容和变压器的等效导纳和等效历史电流源; $C_i$ 为端口电容; $v_{Ci}$ 为电容电压; $i_{Ti}$ 为变压器电感电流。

# 1.2 PET 模块端口解耦等效模型

DAB 模块等效电路可通过消去如图 2 所示的 节点 5~8 获得,其简要步骤如下。首先,对 DAB 模 块列写节点导纳方程,并表示为分块矩阵的形式:

$$\begin{bmatrix} A & B \\ B^{\mathsf{T}} & C \end{bmatrix} \begin{bmatrix} V_{\mathsf{EX}} \\ V_{\mathsf{IN}} \end{bmatrix} = \begin{bmatrix} J_{\mathsf{EX}} \\ J_{\mathsf{IN}} \end{bmatrix} + \begin{bmatrix} I_{\mathsf{EX}} \\ 0 \end{bmatrix} \tag{2}$$

式中: $J_{\text{EX}}$ 、 $J_{\text{EX}}$ 分别为外部节点的注入历史电流列向量和独立电流列向量; $J_{\text{IN}}$ 为内部节点的注入历史电流列向量; $V_{\text{EX}}$ 和 $V_{\text{IN}}$ 分别为外部节点和内部节点的电压列向量;A、B、C均为节点导纳矩阵的分块子矩阵。

其次,利用嵌套快速求解法消去式(2)中内部节点电压 $V_{\mathbb{N}}$ ,有

$$\begin{cases} Y_{\text{EX}} V_{\text{EX}} = J_{\text{S}} + I_{\text{EX}} \\ Y_{\text{EX}} = A - BC^{-1}B^{\text{T}} \\ J_{\text{S}} = J_{\text{EY}} - BC^{-1}J_{\text{IN}} \end{cases}$$

(3)

由文献[25]可知,式(3)所得等效节点导纳方程 具有如下特征:

$$Y_{\text{EX}}V_{\text{EX}} = J_{\text{S}} + I_{\text{EX}} = \begin{bmatrix} 1 & -1 \\ -1 & 1 \end{bmatrix} y_{12} \begin{bmatrix} 1 & -1 \\ -1 & 1 \end{bmatrix} \begin{bmatrix} v_1 \\ v_2 \\ -1 & 1 \end{bmatrix} = \begin{bmatrix} 1 & -1 \\ y_{21} \begin{bmatrix} 1 & -1 \\ -1 & 1 \end{bmatrix} y_{22} \begin{bmatrix} 1 & -1 \\ -1 & 1 \end{bmatrix} \begin{bmatrix} v_1 \\ v_2 \\ v_3 \\ v_4 \end{bmatrix} = \begin{bmatrix} j_{\text{S1}} \begin{bmatrix} 1 \\ -1 \end{bmatrix} + \begin{bmatrix} i_1 \begin{bmatrix} 1 \\ -1 \end{bmatrix} \\ i_2 \begin{bmatrix} 1 \\ -1 \end{bmatrix} \end{bmatrix}$$

$$(4)$$

式中: $y_{11}$ 、 $y_{12}$ 、 $y_{21}$ 、 $y_{22}$ 为节点导纳矩阵的特征元素; $v_1$ ~ $v_4$ 为4个外端子节点的电压; $j_{S1}$ 、 $j_{S2}$ 为短路电流列向量的特征元素; $i_1$ 、 $i_2$ 为DAB模块两侧端口的电流。

这一特性产生的原因是,DAB模块包含隔离变压器,满足严格的端口条件,其节点导纳矩阵表达存在冗余。式(4)所示4阶等效节点导纳方程可用如式(5)所示的2阶短路导纳参数(Y参数)方程,即端口方程表示。

$$\begin{bmatrix} i_{\text{IN}} \\ i_{\text{OUT}} \end{bmatrix} = \begin{bmatrix} Y_{11}^{\text{DAB}} & Y_{12}^{\text{DAB}} \\ Y_{21}^{\text{DAB}} & Y_{22}^{\text{DAB}} \end{bmatrix} \begin{bmatrix} v_{\text{IN}} \\ v_{\text{OUT}} \end{bmatrix} + \begin{bmatrix} i_{\text{SC1}} \\ i_{\text{SC2}} \end{bmatrix}$$

(5)

式中: $v_{\text{IN}}$ 、 $i_{\text{IN}}$ 和 $v_{\text{OUT}}$ 、 $i_{\text{OUT}}$ 分别为 DAB 模块输入侧和输出侧的电压、电流; $Y_{11}^{\text{DAB}}$ 和 $Y_{22}^{\text{DAB}}$ 为端口的输入导纳; $Y_{12}^{\text{DAB}}$ = $Y_{21}^{\text{DAB}}$ 为转移导纳; $i_{\text{SC1}}$ 和 $i_{\text{SC2}}$ 为外端口短路时的 2个端口的短路电流。各参数具有直观的物理意义,其等效电路如附录 A图 A1所示。

式(5)中 DAB 模块等效电路各参数可由附录 B式(B1)所示代数运算获得<sup>[25]</sup>。其中, $q_1 \sim q_5$ 为常数,如附录 B式(B2)所示,由式(1)所示变压器等效导纳  $G_{T11}$ 、 $G_{T12}$ 、 $G_{T21}$ 、 $G_{T22}$ 和开关器件的二值导纳  $G_{ON}$ 、 $G_{OFF}$ 决定。 $K_1^{DAB} \sim K_5^{DAB}$  为符号函数,由图 2 所示的 8 个二值导纳  $G_{H1} \sim G_{H4}$ 、 $G_{L1} \sim G_{L4}$ 的控制信号  $T_{H1} \sim T_{H4}$ 、 $T_{L1} \sim T_{L4}$ 决定,如式(6)所示。

$$\begin{cases} K_{1}^{DAB} = \begin{cases} 1 & T_{H1} \neq T_{H3} \\ 0 & T_{H1} = T_{H3} \end{cases} \\ K_{2}^{DAB} = \begin{cases} 0 & T_{H1} = T_{H3} \stackrel{\times}{\to} T_{L1} = T_{L3} \\ 1 & T_{H1} = T_{L1} \stackrel{\times}{\to} T_{H3}, T_{L1} \neq T_{L3} \\ -1 & T_{H1} = T_{L1} \stackrel{\times}{\to} T_{H3}, T_{L1} \neq T_{L3} \end{cases} \\ K_{3}^{DAB} = \begin{cases} 1 & T_{L1} \neq T_{L3} \\ 0 & T_{L1} = T_{L3} \end{cases} \\ K_{4}^{DAB} = \begin{cases} 0 & T_{H1} = T_{H3} \\ 1 & T_{H1} = 1 \stackrel{\times}{\to} T_{H3} \\ -1 & T_{H1} = 0 \stackrel{\times}{\to} T_{H1} \neq T_{H3} \end{cases} \\ K_{5}^{DAB} = \begin{cases} 0 & T_{L1} = T_{L3} \\ 1 & T_{L1} = 1 \stackrel{\times}{\to} T_{L3} \\ 1 & T_{L1} = 1 \stackrel{\times}{\to} T_{L3} \end{cases} \end{cases}$$

$$\begin{cases} 0 & T_{L1} = T_{L3} \\ T_{L1} = 1 \stackrel{\times}{\to} T_{L3} \neq T_{L3} \end{cases}$$

$$\begin{cases} 0 & T_{L1} = T_{L3} \\ T_{L1} = 0 \stackrel{\times}{\to} T_{L1} \neq T_{L3} \end{cases}$$

$$\begin{cases} 0 & T_{L1} = T_{L3} \\ T_{L1} = 0 \stackrel{\times}{\to} T_{L1} \neq T_{L3} \end{cases}$$

$$\begin{cases} 0 & T_{L1} = T_{L3} \\ T_{L1} = 0 \stackrel{\times}{\to} T_{L1} \neq T_{L3} \end{cases}$$

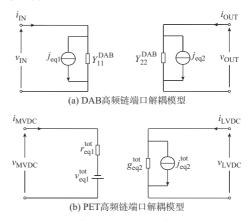

在这一双端口等效电路基础上,为便于DAB模块级联,本文采用文献[25]所提高频链端口解耦算法,将式(5)和附录A图A1所示DAB等效电路进行电容电压约等,所得DAB模块端口方程如式(7)所示。

$$\begin{bmatrix} i_{\text{IN}}(t) \\ i_{\text{OUT}}(t) \end{bmatrix} = \begin{bmatrix} Y_{11}^{\text{DAB}} & Y_{12}^{\text{DAB}} \\ Y_{21}^{\text{DAB}} & Y_{22}^{\text{DAB}} \end{bmatrix} \begin{bmatrix} v_{\text{IN}}(t) \\ v_{\text{OUT}}(t) \end{bmatrix} + \begin{bmatrix} i_{\text{SC1}}(t) \\ i_{\text{SC2}}(t) \end{bmatrix} \approx$$

$$\begin{bmatrix} Y_{11}^{\text{DAB}} & 0 \\ 0 & Y_{22}^{\text{DAB}} \end{bmatrix} \begin{bmatrix} v_{\text{IN}}(t) \\ v_{\text{OUT}}(t) \end{bmatrix} +$$

$$\begin{bmatrix} 0 & Y_{12}^{\text{DAB}} \\ Y_{21}^{\text{DAB}} & 0 \end{bmatrix} \begin{bmatrix} v_{\text{IN}}(t - \Delta t) \\ v_{\text{OUT}}(t - \Delta t) \end{bmatrix} + \begin{bmatrix} i_{\text{SC1}}(t) \\ i_{\text{SC2}}(t) \end{bmatrix} =$$

$$\begin{bmatrix} Y_{11}^{\text{DAB}} & 0 \\ 0 & Y_{22}^{\text{DAB}} \end{bmatrix} \begin{bmatrix} v_{\text{IN}}(t) \\ v_{\text{OUT}}(t) \end{bmatrix} + \begin{bmatrix} j_{\text{eq1}}(t) \\ j_{\text{eq2}}(t) \end{bmatrix}$$

$$(7)$$

式中: $j_{eq}$ 和 $j_{eq2}$ 为2个端口的诺顿等效历史电流源。

DAB模块高频链解耦等效电路如图 3(a)所示, 该方法的仿真精度与数值稳定性已在文献[25,27]中得到证明。

图 3 高频链端口解耦等效模型 Fig. 3 Decoupling equivalent model of high-frequency link port

将输入侧诺顿等效电路转化为戴维南等效电路,并进行串并联侧模块等效参数的求和,可得PET高频链端口解耦模型如图 3(b)所示,各参数表达式如式(8)所示。

$$\begin{cases} r_{\text{eq1}}^{\text{tot}} = \sum_{i=1}^{N} r_{\text{eq1},i} = \sum_{i=1}^{N} \frac{1}{Y_{11,i}^{\text{DAB}}} \\ v_{\text{eq1}}^{\text{tot}} = \sum_{i=1}^{N} v_{\text{eq1},i} = \sum_{i=1}^{N} \frac{j_{\text{eq1},i}}{Y_{11,i}^{\text{DAB}}} \\ g_{\text{eq2}}^{\text{tot}} = \sum_{i=1}^{N} g_{\text{eq2},i} = \sum_{i=1}^{N} Y_{22,i}^{\text{DAB}} \\ j_{\text{eq2}}^{\text{tot}} = \sum_{i=1}^{N} j_{\text{eq2},i} \end{cases}$$

$$(8)$$

式中: $r_{\rm eql}^{\rm tot}$  和  $v_{\rm eql}^{\rm tot}$  分别为 PET 输入侧等效戴维南电阻 和电压源; $g_{\rm eq2}^{\rm tot}$  和  $j_{\rm eq2}^{\rm tot}$  分别为 PET 输出侧诺顿等效电导和电流源; $r_{\rm eq1,i}$  和  $v_{\rm eq1,i}$  分别为第 i 个模块的等效戴维南电阻和电压源; $g_{\rm eq2,i}$  和  $j_{\rm eq1,i}$  为别为第 i 个模块的诺顿等效电导和电流源;N 为 DAB 模块数; $Y_{11,i}^{\rm DAB}$  和  $Y_{22,i}^{\rm DAB}$  为 第 i 个 DAB 模块的二端口输入导纳。

# 1.3 DAB 端口解耦模型二值特性及 PET 端口解耦模型"N+1"特性

由附录 B式(B1)可知, DAB 模块的端口输入导纳  $Y_{11}^{DAB}$ 和  $Y_{22}^{DAB}$ 具有二值特性,由其相邻 H 桥控制信号决定,可记其表达式如下:

$$\begin{cases} Y_{11}^{DAB} = K_1^{DAB} Q_1 + \overline{K_1^{DAB}} Q_2 \\ Y_{22}^{DAB} = K_3^{DAB} Q_3 + \overline{K_3^{DAB}} Q_4 \end{cases}$$

(9)

式中: $Q_1 \sim Q_4$ 为常数,可在程序开始计算获得; $\overline{K_1^{\text{DAB}}}$ 和 $\overline{K_3^{\text{DAB}}}$ 分别表示 $\overline{K_1^{\text{DAB}}}$ 和 $\overline{K_3^{\text{DAB}}}$ 的逻辑非。

1.2节给出了DAB模块二端口等效电路的输入导纳二值特性的数值解释。为进一步揭示二值特性产生的原因,本节从等效电路构建角度对其物理意义进行阐述与分析。

由 Y 参数定义可得, DAB 模块二端口等效电路输入导纳  $Y_{22}^{DAB}$  和  $Y_{22}^{DAB}$  可以通过将对侧端口短路,内部电流源置零后,求各端口电流与电压之比获得,如式(10) 所示。

$$\begin{cases} Y_{11}^{\text{DAB}} = \frac{i_1}{v_1} \Big|_{v_2 = 0} \\ Y_{22}^{\text{DAB}} = \frac{i_2}{v_2} \Big|_{v_2 = 0} \end{cases}$$

(10)

以  $Y_{11}^{DAB}$  为例,其获取过程如附录 A 图 A2 所示。 其中, $G_{T11}$ 、 $G_{T12}$ 、 $G_{T22}$  为变压器等效导纳, $G_{C1}$ 和  $G_{C2}$  为电容的等效电导,如式(1)所示,均为常数。  $G_{H1}\sim G_{H4}$ 、 $G_{L1}\sim G_{L4}$ 为由触发信号  $T_{H1}\sim T_{H4}$ 、 $T_{L1}\sim T_{L4}$  控制的二值导纳值,具有时变特性。

在非闭锁运行状态下,DAB模块的H桥同桥臂互补,故有:

$$G_{L1} + G_{L2} = G_{L3} + G_{L4} = G_{ON} + G_{OFF}$$

(11)

式中: $G_{ON}$ 通常取100 S: $G_{OFF}$ 通常取1e<sup>-6</sup> S<sub>o</sub>

因此, 附录 A 图 A2右侧粉色框内电路的等效电导  $Y_{\text{end}}$ 恒定为:

$$Y_{\rm eql} = \frac{G_{\rm ON} + G_{\rm OFF}}{2} \tag{12}$$

$G_{T11}$ 、 $G_{T12}$ 、 $G_{T22}$ 为定值,故左侧 H 桥交流端口等效电导  $Y_{eq2}$ 也恒定。 $Y_{11}^{DAB}$  仅由其相邻 H 桥触发信号  $T_{H1} \sim T_{H4}$ 决定,分为  $T_{H1} \neq T_{H3}$ 和  $T_{H1} = T_{H3}$ 两种情况,可表示为:

$$Y_{11}^{\text{DAB}} = K_1^{\text{DAB}} Q_1 + \overline{K_1^{\text{DAB}}} Q_2$$

(13)

同理,有

$$Y_{22}^{\text{DAB}} = K_3^{\text{DAB}} Q_3 + \overline{K_3^{\text{DAB}}} Q_4$$

(14)

该结论与由直接数值计算所得式(9)一致。

综上,虽然 DAB 模块包含 8个 IGBT/二极管反并联开关组,但由于 H桥固定的拓扑结构和开关方式,其输入导纳并不会有 2<sup>8</sup>种可能情况,而是表现为由同侧 H桥开关信号决定的二值特性。

利用单模块输入导纳的二值特性,将式(9)代人式(8)可得.

$$\begin{cases} r_{\text{eql}}^{\text{tot}} = \sum_{i=1}^{N} \frac{1}{Y_{11,i}^{\text{DAB}}} = \frac{n_1}{Q_1} + \frac{N - n_1}{Q_2} \\ g_{\text{eq2}}^{\text{tot}} = \sum_{i=1}^{N} Y_{22,i}^{\text{DAB}} = n_2 Q_3 + (N - n_2) Q_4 \end{cases}$$

(15)

式中: $n_1$ 和 $n_2$ 分别表示满足 $T_{H1} \neq T_{H3}$ 和 $T_{L1} \neq T_{L3}$ 的DAB模块数, $n_1, n_2 \in \{0, 1, \dots, N\}$ 。

因此,包含N个模块的PET系统,其输入电阻  $r_{\rm eql}^{\rm tot}$ 和输出电导 $g_{\rm eql}^{\rm tot}$ 仅有N+1种可能取值,可通过参数存储和对触发信号的逻辑判断直接获取。

#### 1.4 内部信息更新

将图 3(b)所示的 PET 等效模型与外电路结合,进行 EMT 解算结束之后,可获得中压直流母线电压  $v_{\text{MVDC}}$ 、电流  $i_{\text{MVDC}}$ 和低压直流母线电压  $v_{\text{LVDC}}$ 、电流  $i_{\text{LVDC}}$ ,如图 3(b)所示。然后,需要对各模块端口及内部节点电压进行更新,用于下一步长的迭代计算。

各模块共用输入侧电流  $i_{\text{IN}}=i_{\text{MVDC}}$  和输出侧电压  $v_{\text{OUT}}=v_{\text{LVDC}}$ 。因此,各模块端口电压(即电容电压)表达式为:

$$\begin{bmatrix} v_{\text{C1}} \\ v_{\text{C2}} \end{bmatrix} = \begin{bmatrix} \frac{1}{Y_{11}^{\text{DAB}}} & 0 \\ 0 & 1 \end{bmatrix} \begin{bmatrix} i_{\text{IN}} \\ v_{\text{OUT}} \end{bmatrix} + \begin{bmatrix} -1 \\ 0 \end{bmatrix} v_{\text{eq1}} \quad (16)$$

式中:ven 为模块输入侧戴维南等效电压源,如式(8)

所示。

在文献[25]中,变压器端口电压 $v_{T1}$ 和 $v_{T2}$ 的更新仍需要进行矩阵乘法与求逆运算,会给实时仿真带来较大负担。本节将DAB模块等效电路参数求解过程中节点导纳方程预处理的思想引入对变压器端口电压的更新过程中,所得端口电压更新式如下:

$$\begin{cases} v_{\text{T1}} = 2(q_1 - q_2) j_{\text{T1}} + 4q_3 j_{\text{T2}} - K_4^{\text{DAB}} (q_1 - q_2) (G_{\text{OFF}} - G_{\text{ON}}) v_{\text{IN}} - K_5^{\text{DAB}} 2q_3 (G_{\text{OFF}} - G_{\text{ON}}) v_{\text{OUT}} \\ v_{\text{OUT}} v_{\text{T2}} = 4q_3 j_{\text{T1}} + 2(q_4 - q_5) j_{\text{T2}} - K_4^{\text{DAB}} 2q_3 (G_{\text{OFF}} - G_{\text{ON}}) v_{\text{IN}} - K_5^{\text{DAB}} (q_4 - q_5) (G_{\text{OFF}} - G_{\text{ON}}) v_{\text{OUT}} \end{cases}$$

$$(17)$$

其中,仅包含对常数与符号函数的代数运算,计算负荷大幅简化,更便于实时仿真的实现。

# 2 DAB型PET实时低耗等效仿真算法

#### 2.1 基于有限导纳存储的低内存占用 EMT 解算

基于二值开关电阻模型的电力电子系统在执行 EMT解算时,面临节点导纳矩阵时变问题,需进行 大量矩阵乘法与求逆运算,不利于实时仿真的实 现。因此,本节提出一种基于有限导纳存储的低内 存占用EMT解算方案。

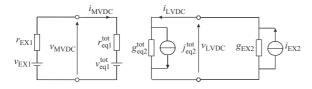

为便于EMT解算描述,设DAB型PET输入侧的外电路为戴维南等效电路(包含戴维南等效电阻  $r_{\text{EXI}}$ 和等效电压源  $v_{\text{EXI}}$ ),输出侧外电路为诺顿等效电路(包含诺顿等效电导  $g_{\text{EX2}}$ 和等效电流源  $i_{\text{EX2}}$ ),结合图 3(b)所示 PET 高频链端口解耦模型,可得EMT解算电路如图 4所示。

图 4 EMT解算等效电路 Fig. 4 Equivalent circuit for EMT solving

求解该电路可得:

$$\begin{bmatrix} v_{\text{MVDC}} \\ i_{\text{MVDC}} \end{bmatrix} = \begin{bmatrix} \frac{r_{\text{eql}}^{\text{tot}}}{r_{\text{EX1}} + r_{\text{eql}}^{\text{tot}}} & \frac{-r_{\text{EX1}}}{r_{\text{EX1}} + r_{\text{eql}}^{\text{tot}}} \\ \frac{1}{r_{\text{EX1}} + r_{\text{eql}}^{\text{tot}}} & \frac{1}{r_{\text{EX1}} + r_{\text{eql}}^{\text{tot}}} \end{bmatrix} \begin{bmatrix} v_{\text{EX1}} \\ v_{\text{eql}}^{\text{tot}} \end{bmatrix} \quad (18)$$

$$\begin{bmatrix} v_{\text{LVDC}} \\ i_{\text{LVDC}} \end{bmatrix} = \begin{bmatrix} \frac{1}{g_{\text{EX2}} + g_{\text{eq2}}^{\text{tot}}} & \frac{-1}{g_{\text{EX2}} + g_{\text{eq2}}^{\text{tot}}} \\ \frac{g_{\text{eq2}}^{\text{tot}}}{g_{\text{EX2}} + g_{\text{eq2}}^{\text{tot}}} & \frac{g_{\text{EX2}}}{g_{\text{EX2}} + g_{\text{eq2}}^{\text{tot}}} \end{bmatrix} \begin{bmatrix} i_{\text{EX2}} \\ j_{\text{eq2}}^{\text{tot}} \\ j_{\text{eq2}}^{\text{tot}} \end{bmatrix} \quad (19)$$

从式(18)和式(19)可知,一方面,PET的高频链解耦等效模型仅包含2条支路、4个节点,使得EMT解算矩阵阶数大幅减小,降低了求解复杂度;另一方面,由式(15)所示PET等值电阻/电导的N+1特性可知,式(18)和式(19)中系数矩阵也通过有限的参数存储(6N+6个)来避免除法运算,可大幅减小对存储量的需求。

当系统外电路复杂时,其EMT解算系数矩阵仍可用少量内存占用实现节点导纳逆矩阵的存储,从而使得二值电阻开关模型可以用于大规模DAB型PET系统的实时仿真中。

# 2.2 电磁暂态等效算法的矩阵表达

为方便实时仿真算法逻辑的实现,本节分别对 DAB型PET等效电路参数求解、EMT解算、内部 信息更新3个过程进行梳理,建立其矩阵表达形式。

# 1)等效电路参数求解

由 2.1 节可知, DAB 模块等效参数计算仅包含 串联侧等效历史电压源和并联侧等效历史电流源的 求解,记为  $v_{eq1}$  和  $j_{eq2}$ 。将式(1)和附录 B式(B1)代人式(7)可得附录 B式(B3),记为:

$S_{eq}(t) = P_1 v_C(t - \Delta t) + P_2 i_T(t - \Delta t)$  (20) 式中: $S_{eq} = [v_{eq1}, j_{eq2}]^T$ 为 DAB 模块等效历史源列向量; $i_T$ 为变压器原副边电流向量; $v_C$ 为电容电压向量; $P_1$ 和  $P_2$ 为由常数与符号函数决定的系数矩阵。之后,按照式(8)对各模块等效历史电压/电流源求和,即可获得 PET 的等效电路参数。

### 2)EMT解算

记式(18)和式(19)所示EMT解算过程为:

$$\begin{cases}

S_{\text{MVDC}}(t) = P_3 v_{\text{S,EQ}}(t) \\

S_{\text{LVDC}}(t) = P_4 i_{\text{S,EQ}}(t)

\end{cases}$$

(21)

式中: $S_{\text{MVDC}} = [v_{\text{MVDC}}, i_{\text{MVDC}}]^{\text{T}}$ 和  $S_{\text{LVDC}} = [v_{\text{LVDC}}, i_{\text{LVDC}}]^{\text{T}}$  分别为 PET 输入和输出端口电压、电流信息; $v_{\text{S,EQ}}$  和  $i_{\text{S,EQ}}$  分别为外部独立源与等效历史源; $P_{3}$  和  $P_{4}$  为 2 阶系数矩阵。

#### 3)内部信息更新

记式(16)所示模块电容端口电压更新表达式为:

$$v_{\rm C}(t) = P_5 S_{\rm IO}(t) + P_6 v_{\rm eq1}(t)$$

(22)

式中: $S_{\text{IO}} = [i_{\text{IN}}, v_{\text{OUT}}]^{\text{T}} = [i_{\text{MVDC}}, v_{\text{LVDC}}]^{\text{T}}$ ,由式(21)获得: $P_5$ 和 $P_6$ 分别为 2×2和2×1的系数矩阵。

变压器端口电压更新表达式如式(17)所示,将式(1)和式(22)代人式(17),可得附录B式(B4)所示具体表达式,记为:

$v_{\rm T}(t) = P_7 i_{\rm T}(t - \Delta t) + P_8 S_{\rm IO}(t) + P_9 v_{\rm eq1}(t)$  (23) 式中: $v_{\rm T} = [v_{\rm T1}, v_{\rm T2}]^{\rm T}$ 为变压器原副边电压; $P_7 \sim P_9$ 为系数矩阵,各元素均可通过常数与符号函数的逻辑

运算得到。

由图2可知,变压器电流表达式为:

$$egin{aligned} m{i}_{\mathrm{T}}(t) &= m{G}_{\mathrm{T}} m{v}_{\mathrm{T}}(t) - m{j}_{\mathrm{T}}(t) = m{G}_{\mathrm{T}} m{P}_{\mathrm{8}} m{S}_{\mathrm{1O}}(t) + \\ & (m{G}_{\mathrm{T}} m{P}_{\mathrm{7}} + E) m{i}_{\mathrm{T}}(t - \Delta t) + m{G}_{\mathrm{T}} m{P}_{\mathrm{9}} m{v}_{\mathrm{eq1}}(t) igtriangledown \end{aligned}$$

$P_{10}S_{10}(t) + P_{11}i_{T}(t-\Delta t) + P_{12}v_{eq1}(t)$  (24) 式中: $j_{T} = [j_{T1}, j_{T2}]^{T}$ 为变压器原副边等效历史电流源,如图1所示;E为单位矩阵; $P_{10} \sim P_{12}$ 为系数矩阵,各元素均可通过常数与符号函数的逻辑运算得到。

综合式(22)一式(24),可列写内部电气信息反

演过程矩阵表达式如下:

$$\begin{bmatrix} \mathbf{v}_{c}(t) \\ \mathbf{v}_{T}(t) \\ \mathbf{i}_{T}(t) \end{bmatrix} = \begin{bmatrix} \mathbf{P}_{5} & \mathbf{0} & \mathbf{P}_{6} \\ \mathbf{P}_{8} & \mathbf{P}_{7} & \mathbf{P}_{9} \\ \mathbf{P}_{10} & \mathbf{P}_{11} & \mathbf{P}_{12} \end{bmatrix}_{6 \times 5} \begin{bmatrix} \mathbf{S}_{10}(t) \\ \mathbf{i}_{T}(t - \Delta t) \\ \mathbf{v}_{eq1}(t) \end{bmatrix}$$

(25)

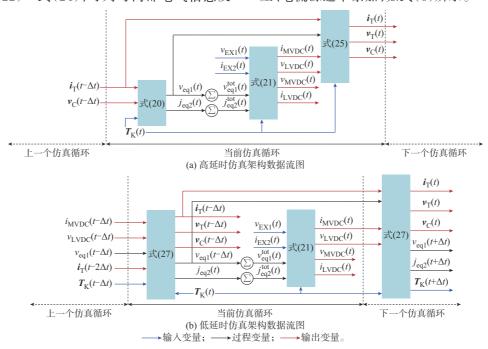

### 2.3 基于紧凑型计算逻辑的低延时仿真框架

按 2.2 节中 3 个步骤绘制数据流图,如图 5 (a)所示。图中:  $T_{K}$ =[ $T_{H1}$ , $T_{H3}$ , $T_{L1}$ , $T_{L3}$ ]为触发信号组,用于表征各模块控制信号;  $\sum$ 表示将各模块等效电压、电流源逐个累加,如式(8)所示。

图 5 实时仿真数据流图 Fig. 5 Data flow diagram of real-time simulation

图 5(a) 所示的算法框架与离线仿真平台 PSCAD/EMTDC类似,在每一步长仿真中均包含 3个阶段:电力网络等值参数计算,如式(20)所示;电力网络求解,如式(21)所示;计算结果输出与电气信息更新,如式(25)所示。这 3个步骤在 PSCAD 仿真流程中分别对应 DSDYN、EMTDC 解算、DSDOUT 这 3个环节<sup>[28]</sup>。同时,这 3个阶段需要串行执行,延时较长。

为缩短实时仿真每步的时钟消耗,本节提出一种基于紧凑型计算逻辑的低延时仿真框架。

首先,考虑到PET外电路的复杂性,保留以戴维南/诺顿等效电路参与EMT解算的独立过程,即维持式(21)所示EMT解算不变。当外电路改变,只需对这一部分进行修改即可。

其次,上一步的内部电气信息更新结果为下一步的等值参数计算的输入。因此,可将式(25)代入

式(20)得:

$$S_{eq}(t + \Delta t) = P_{1}v_{C}(t) + P_{2}i_{T}(t) = [P_{1}P_{5} + P_{2}P_{10}]S_{IO}(t) + P_{2}P_{11}i_{T}(t - \Delta t) + [P_{1}P_{6} + P_{2}P_{12}]v_{eq1}(t) = P_{13}S_{IO}(t) + P_{14}i_{T}(t - \Delta t) + P_{15}v_{eq1}(t) \triangleq [P_{13} P_{14} P_{15}]_{2 \times 5} \begin{bmatrix} S_{IO}(t) \\ i_{T}(t - \Delta t) \end{bmatrix}$$

(26)

式中: $P_{13}\sim P_{15}$ 为由 $P_{1}\sim P_{12}$ 计算所得的参数矩阵。

式(25)和式(26)共用输入变量,可将两式合并:

$$\begin{bmatrix} \mathbf{v}_{C}(t) \\ \mathbf{v}_{T}(t) \\ \mathbf{i}_{T}(t) \\ \mathbf{S}_{eq}(t+\Delta t) \end{bmatrix} = \begin{bmatrix} \mathbf{P}_{5} & \mathbf{0} & \mathbf{P}_{6} \\ \mathbf{P}_{8} & \mathbf{P}_{7} & \mathbf{P}_{9} \\ \mathbf{P}_{10} & \mathbf{P}_{11} & \mathbf{P}_{12} \\ \mathbf{P}_{13} & \mathbf{P}_{14} & \mathbf{P}_{15} \end{bmatrix}_{8 \times 5} \begin{bmatrix} \mathbf{S}_{10}(t) \\ \mathbf{i}_{T}(t-\Delta t) \\ v_{eq1}(t) \end{bmatrix}$$

(27)

所提低延时仿真架构的数据流图如图 5(b)所 示,上一步的内部电气信息更新与下一步的等值电 压、电流源计算并行执行,在不损失仿真精度的同 时,缩短了所需时钟数。

# 实时仿真硬件实现

#### 3.1 数据格式

浮点数和定点数为FPGA常用的两种数据格 式。浮点数数据范围广、精度高、存储需求小,定点 数加法执行便捷、时钟消耗少。因此,本文使用浮点 数与定点数混合的数据表示方法。乘法运算使用 32 位 IEEE 754 标准的浮点数实现,每个乘法器占 用2个DSP48E资源;加减法运算使用60位定点数 (24位整数、36位小数)实现,占用一定的逻辑片资 源;数据的存储以浮点数格式完成,减少内存消耗。 浮点数与定点数之间的相互转换可通过 Xilinx 自带 的 IP 核 (intellectual property core) 实现。

#### 3.2 矩阵-向量乘法的实现

如图 5(b)所示,本文所提PET实时低耗仿真算 法仅包含式(27)所示的1个8×5矩阵乘法和式 (21) 所示的 2 个 2×2 矩阵乘法。 经典的 FPGA 矩 阵-向量乘法(matrix-vector multiplication, MVM)实 现方式如附录 A 图 A3(a) 所示, 可通过 m 个乘法器  $\mathfrak{L}_{n+1}$ 个时钟实现 $m \times n$ 矩阵A与n维列向量b的 乘法[20-21]。

考虑矩阵中的0、1、-1元素乘法可直接由逻辑 运算获得,式(21)与式(27)所示低阶矩阵中仅分别 包含8次和31次乘法运算。为节省时钟占用,本文 采用如附录 A 图 A3(b) 所示的代数乘法方式,将矩 阵-向量运算中的所有乘法运算在一个时钟直接完 成。同时,由于所需存储的矩阵元素很少,可直接使 用寄存器代替只读存储器(ROM)存储。

该方法增加了对DSP48E资源的消耗,但由于 乘法运算很少,DSP48E并不会成为制约仿真规模 的主要因素。该结论将在4.3节中予以验证。

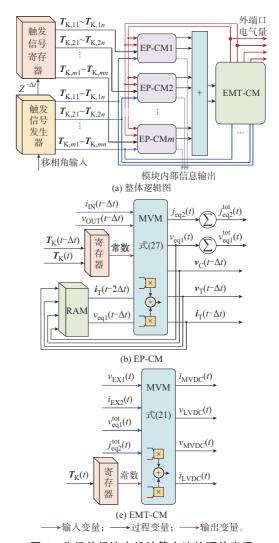

### 3.3 多模块分组并行的流水线设计

在获得各DAB模型输入侧的戴维南等效电压 和输出侧的诺顿等效电流源后,需要对其进行求和 运算,如式(8)所示。综合考虑仿真资源与时钟需 求,本文设计了如图 6(a) 所示的分组并行流水线计 算方案。该方案包含 m 个 等值参数 计算模块 (equivalent parameter calculation module, EP-CM) 和 1 个 EMT 解 算 模 块 (EMT calculation module, EMT-CM),如图 6(b)和(c)所示。图中: $Z^{-\Delta t}$ 表示 控制器触发延时。

首先,FPGA中的触发信号生成器接受上位机

分组并行流水线计算方法的硬件实现 Fig. 6 Hardware implementation of packet-based parallel pipeline computing method

输入的移相控制信号,生成各DAB模块的触发信号 组  $T_{K}$ ,并将其分为 m 组,记第 i 组信号为  $T_{K,ii} \sim T_{K,in}$  $(i \in [1, m])$ 。其次,每组第  $1 \sim n \uparrow DAB$  模块的  $T_{K,n}$  $(i \in [1, n])$ 按照时钟被依次并行送入对应的第i个 EP-CM 模块,进行如式(27)所示的计算,实现流水 线作业。组内各DAB模块等效电压/电流源的求和 分别在各自EP-CM模块内部完成。然后,各流水线 所得求和结果经加法器合并,完成DAB型PET等 效电路参数的求解。最后,由EMT-CM模块完成 式(21)所示电路解算功能。

通过上述方案,包含 $N=m\times n$ 个DAB模块的 PET 系统的单步仿真可在 17+n个时钟内完成,硬 件资源占用量将随 m 线性增加。同时,用户可以根 据仿真步长与硬件资源的实际需求与限制,灵活调 整m和n的取值,获得最优仿真方案。

# 4 仿真验证

#### 4.1 仿真环境

为验证所提 DAB型 PET 实时低耗等效仿真算法的有效性,本文在 RT-LAB上基于 Verilog 语言开发了 PET 实时等效仿真模型,平台架构如附录 A图 A4 所示。

PC 机上配置 RT-LAB 仿真软件, 仿真机使用 OP5700, 内含一台 32 位 Intel Xeon E5 CPU 处理器 和一块 Xilinx Virtex-7 FPGA、485T 板卡, FPGA 时 钟频率为 100 MHz。CPU 处理器用于移相角生成; FPGA 完成脉宽调制 (PWM) 信号生成和主电路解算。PC 机与 OP5700 之间通过 TCP/IP 协议通信, OP5700 内部的 CPU 与 FPGA 之间通过 PCIE 协议通信。为方便后续模型的扩展,本文设置 CPU 控制系统步长为 10 μs, FPGA 侧实时等效模型仿真步长为 250 ns。

# 4.2 仿真精度测试

本节搭建 DAB型 PET 实时等效模型,与使用 PSCAD/EMTDC 库元件构建的详细模型进行对比,系统参数如表 1 所示。PET 的输入侧采用戴维南等效电路,输出侧采用电阻负载,控制方式为双移相控制,内移相角设置恒定值为 9°。

表 1 实时仿真系统参数 Table 1 Parameters of real-time simulation system

| 参数                           | 数值              | 参数                    | 数值              |

|------------------------------|-----------------|-----------------------|-----------------|

| 中压直流母线电压 $v_{\mathrm{MVDC}}$ | 96 kV           | 输入侧电容 $C_1$           | 2 mF            |

| 低压直流母线电压 $v_{\mathrm{LVDC}}$ | $1~\mathrm{kV}$ | 输出侧电容 C <sub>2</sub>  | $1~\mathrm{mF}$ |

| 级联模块数                        | 48              | 辅助电感 $L_{\mathrm{T}}$ | 10 μΗ           |

| 高频变压器频率                      | 10 kHz          | 变压器变比 k               | 2:1             |

设置系统工况如下:

$1)0\sim0.2 \text{ s}$ ,系统启动,负载电阻为  $0.5 \Omega$ ,  $v_{\text{LVDC}}$  参考值为 1.0 p.u.;

2)0.2~0.4 s,稳态运行;

3)0.4 s,功率跃变, v<sub>LVDC</sub>参考值降低为 0.8 p.u.;

4) 0.7 s, 负载突变, 负载电阻由 0.5 Ω突变为 0.25 Ω:

#### 5) 1 s, 仿真结束。

不同工况下,PSCAD 离线详细模型与实时等效模型的低压直流母线电压  $v_{\text{LVDC}}$  波形如附录 A 图 A5 所示。在各过程中,最大相对误差如下:1)启动阶段, $v_{\text{LVDC}}$  经 0.14 s上升到参考值 1 kV,最大相对误差为 1.3%;2)0.4 s输出电压参考值改变,经短暂过渡过程,系统进入新的稳态, $v_{\text{LVDC}}$  变为 0.8 kV,最大相对误差为 1.8%;3)0.7 s负载突变时, $v_{\text{LVDC}}$  急速下降,两类模型最低点电压分别为 0.647 kV 和 0.648 kV,最大相对误差为 1.5%。

为反映所建实时等效模型对系统内部特性的拟合效果,绘制变压器电压、电流波形如附录 A 图 A6 所示。由图可知,所建实时等效模型变压器电压、电流波形与离线详细模型基本一致,最大相对误差小于2%。同时,变压器电压为近似矩形波,不会出现 L/C模型虚拟损耗导致的波形畸变。

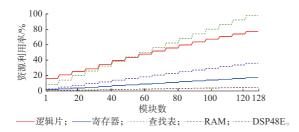

#### 4.3 资源消耗测试

为测试本文所提实时低耗仿真方法的资源占用率,本节建立不同模块数 DAB型 PET 250 ns 实时等效仿真模型,测试其各类资源占用,如表 2 所示。绘制其各类资源占比图,如图 7 所示。

表 2 不同 DAB 模块数 PET 实时仿真硬件资源占用

Table 2 Hardware resource occupancy of real-time simulation for PET with different numbers of DAB modules

| DAB模 | 逻辑片(总数:75 900) |       | 寄存器(总数: 607 200) |       | 查找表(总数: 303 600) |       | RAM(总数: 2 060) |      | DSP48E(总数:2 800) |       |

|------|----------------|-------|------------------|-------|------------------|-------|----------------|------|------------------|-------|

| 块数   | 个数             | 占比/%  | 个数               | 占比/%  | 个数               | 占比/%  | 个数             | 占比/% | 个数               | 占比/%  |

| 8    | 11 996         | 15.81 | 10 026           | 1.65  | 24 392           | 8.03  | 6              | 0.29 | 78               | 2.79  |

| 16   | 15 840         | 20.87 | 16 256           | 2.68  | 42 363           | 13.95 | 12             | 0.58 | 140              | 5.00  |

| 24   | 19 229         | 25.33 | 22 485           | 3.70  | 60 352           | 19.88 | 18             | 0.87 | 202              | 7.21  |

| 32   | 21 817         | 28.74 | 28 834           | 4.75  | 78 223           | 25.77 | 24             | 1.17 | 264              | 9.43  |

| 40   | 26 224         | 34.55 | 35 588           | 5.86  | 97 453           | 32.10 | 30             | 1.46 | 326              | 11.64 |

| 48   | 30 036         | 39.57 | 41 922           | 6.90  | 115 690          | 38.11 | 36             | 1.75 | 388              | 13.86 |

| 96   | 48 333         | 63.68 | 79 206           | 13.04 | 225 112          | 74.15 | 72             | 3.50 | 760              | 27.14 |

| 128  | 58 624         | 77.24 | 104 062          | 17.14 | 298 060          | 98.18 | 96             | 4.66 | 1 008            | 36.00 |

由于FPGA 主频为 100 MHz, 实时仿真系统步长为 250 ns, 即每个仿真步长应在 25 个时钟内完成。由 3.3 节可知, 本文所提分组并行解算模式下,

单步长仿真消耗时钟为17+n,故n=8,如图6所示的每个等值参数计算模块最多可执行8个模块的解算。因此,本节测试模块数取8的整数倍,即使实际

图 7 PET 实时仿真硬件资源利用率 Fig. 7 Hardware resource utilization of real-time simulation for PET

模块数不足8的整数倍,也应按整数倍确定资源。

由图 7和表 2数据可知,随着模块数的上升,各类资源均呈现阶梯线性增加。每增加 8个 DAB 模块(即一个等值参数计算模块),逻辑片(Slice)资源增加 3 100个(4.08%),寄存器(Register)资源约增加 6 300个(1.04%),查找表(LUT)资源约增加 18 244个(6.01%),随机存取存储器(RAM)资源增加 6个(0.29%),乘法器 DSP48E 资源增加 62个(2.21%)。

因此,RAM资源与乘法器DSP48E资源占用很少,不是限制仿真规模的主要因素。查找表资源与逻辑片资源增加较快,当模块数达128时,查找表资源占用达98.18%,仿真规模无法继续增加。

# 4.4 算法性能分析

本文所提实时低耗等效建模方法借鉴了文献[25]节点导纳方程预处理与电容端口解耦的思路,获得了仅包含4个外端子节点、2条支路的PET等效电路。区别于文献[25],所提方法考虑了PET实时仿真模型对存储内存、仿真延时、硬件资源的需求,进行了如下优化设计。

1)基于有限导纳存储的低内存占用 EMT 解算方案。利用 DAB 模块拓扑及控制特征,构建了如图 3(a)所示的单个 DAB 模块等值电路,其等效电导表现为受开关信号控制的二值特性;接着,构建 N个 DAB 模块的 PET 高频链端口解耦等效模型,如图 3(b)所示,输入电阻和输出电导各仅有 N+1种可能取值。同时,大规模节点的 EMT 解算过程被等效为如式(18)和式(19)所示的低阶矩阵解算。在此基础上,通过有限的导纳逆矩阵存储,有效克服了由开关信号二值电阻模型带来的节点导纳矩阵时变问题。

2)基于紧凑型计算逻辑的低延时仿真框架。通过对等值计算流程的矩阵化梳理与运算,将传统EMT解算的"电力网络参数计算""电力网络求解""网络内部电气信息更新"3个步骤中,前一时步"网

络内部电气信息更新"和后一时步的"电力网络参数计算"2个步骤并行,获得了低延时仿真框架如图 5(b)所示,大幅缩减了仿真耗时。

3)多模块分组并行的流水线设计。利用各模块等效电路求解过程的高度可并行性,将模块分组和流水线排列,通过时分复用的方式,使得同组内不同模块的解算过程共用相同的计算资源,有效降低了对计算硬件资源的需求。

需要注意的是,本文所提实时低耗等效建模算法围绕ISOP型DAB高频链展开,该算法同样可适用于其他模块类型和拓扑连接方式的PET系统。同时,上述存储内存、仿真延时、硬件资源方面的优化方法也可为其他电力电子系统的实时仿真提供参考。

为进一步揭示本文所提实时低耗等效建模方案与其他实时仿真方法的区别,本节对比了文献[18]所提基于 RT-LAB 的库元件和 eHS 解算器的详细仿真模型(detailed model,DM)、文献[20]所提基于响应匹配和紧凑型 EMT 解算框架的 PET 等效模型 (equivalent model 1,EM1)、文献[11]所提高并行度等效模型(EM2)以及本文所提低耗等效模型(low-consumption equivalent model,LEM),对比结果如表3和表4所示。

表 3 不同 PET 实时仿真模型具体指标对比

Table 3 Comparison of specific indicators of different real-time simulation models for PET

| 模型  | 单板最大仿真DAB模块数 | 最小仿真步长/ns |

|-----|--------------|-----------|

| DM  | 3            | 800.0     |

| EM1 | 6            | 237.5     |

| EM2 | 42           | 400.0     |

| LEM | 128          | 250.0     |

表 4 不同 PET 实时仿真模型整体性能对比 Table 4 Comparison of overall performance of different real-time simulation models for PET

| 模型  | 仿真精度         | 大规模仿真<br>能力  | 高频系统仿<br>真能力 | 可扩展性         |

|-----|--------------|--------------|--------------|--------------|

| DM  | ****         | ****         | ***          | ****         |

| EM1 | <b>★★★</b> ☆ | ***          | ****         | <b>★</b> ★★☆ |

| EM2 | ****         | <b>★</b> ★★☆ | ****         | <b>★</b> ★★☆ |

| LEM | ****         | ****         | ****         | <b>★</b> ★★☆ |

注:更多的★表示更优的性能。

在仿真精度方面,DM采用L/C开关模型,EM1采用了基于响应匹配算法的L/C模型,受限于虚拟功率损耗问题,其精度低于采用二值电阻模型的EM2和LEM。在大规模系统仿真能力方面,DM模型和EM1模型仅可支持数个DAB模块规模的仿

真,仿真规模受限,EM2模型最大单板可支持50个模块左右的仿真,而本文所提LEM由于硬件资源和存储内存等方面的优化,最大仿真规模可达上百模块。在高频系统仿真能力方面,DM模型的最小仿真步长为800 ns,但高频段下L/C模型虚拟功率损耗问题更加严重,适用性受限;EM1、EM2和LEM模型最小仿真步长可限制在400 ns以下,可有效支持高频DAB的仿真。在可扩展性方面,DM由于基于分立元件构建,可灵活修改拓扑,EM1、EM2和LEM需要对给定拓扑进行等值处理,可扩展性略低。

## 5 结语

本文通过数值计算和物理意义分析,证明了DAB模块高频链端口等效模型输入导纳具有二值特性,在此基础上构建了具有"N+1"特性的PET高频链端口解耦模型。DAB型PET的这一特性表明,对于拓扑和参数固定的电力电子系统,其外端口等效电路的导纳/阻抗仅包含有限可能解,通过外端口等效模型构建和等效参数分析,可以有效解决二值开关电阻模型引起的导纳时变问题,为大规模电力电子系统的实时仿真提供算法支撑。

本文提出了基于有限导纳存储的低内存占用 EMT解算方案、紧凑型计算逻辑的低延时仿真框架、多模块分组并行的流水线设计,可有效降低 PET实时仿真模型对存储内存、仿真时钟、硬件资源的要求。该设计思路和框架可为其他模块化级联 拓扑的实时仿真提供借鉴。

本文所提实时仿真方法仅适用于DAB型PET 非闭锁工况的仿真,其闭锁工况需要考虑二极管的 插值等过程,有待进一步解决。同时,诸如多有源桥 型PET、大规模新能源经电压源变流器并网系统的 其他更复杂的电力电子系统的实时仿真方法有待进 一步探索。

附录见本刊网络版(http://www.aeps-info.com/aeps/ch/index.aspx),扫英文摘要后二维码可以阅读网络全文。

#### 参考文献

- [1] 李凯,赵争鸣,袁立强,等.面向交直流混合配电系统的多端口电力电子变压器研究综述[J].高电压技术,2021,47(4):1233-1250.

- LI Kai, ZHAO Zhengming, YUAN Liqiang, et al. Overview on research of multi-port power electronic transformer oriented for AC/DC hybrid distribution grid [J]. High Voltage Engineering,

- 2021, 47(4): 1233-1250.

- [2] 孙凯,卢世蕾,易哲嫄,等.面向电力电子变压器应用的大容量高频变压器技术综述[J].中国电机工程学报,2021,41(24):8531-8546.

- SUN Kai, LU Shilei, YI Zheyuan, et al. A review of high-power high-frequency transformer technology for power electronic transformer applications[J]. Proceedings of the CSEE, 2021, 41(24): 8531-8546.

- [3] 郑通,王奎,郑泽东,等.基于MMC拓扑的电力电子变压器研究综述[J].中国电机工程学报,2022,42(15):5630-5649.

ZHENG Tong, WANG Kui, ZHENG Zedong, et al. Review of power electronic transformers based on modular multilevel converters[J]. Proceedings of the CSEE, 2022, 42(15): 5630-5640.

- [4] SHE X, HUANG A Q, BURGOS R. Review of solid-state transformer technologies and their application in power distribution systems [J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2013, 1(3): 186-198.

- [5] HUBER J E, KOLAR J W. Optimum number of cascaded cells for high-power medium-voltage AC-DC converters [J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2017, 5(1): 213-232.

- [6] 郭琦,卢远宏.新型电力系统的建模仿真关键技术及展望[J].电力系统自动化,2022,46(10):18-32. GUO Qi, LU Yuanhong. Key technologies and prospects of modeling and simulation of new power system[J]. Automation of Electric Power Systems, 2022, 46(10): 18-32.

- [7] 徐晋,汪可友,李国杰.电力电子设备及含电力电子设备电力系统实时仿真研究综述[J].电力系统自动化,2022,46(10):3-17. XU Jin, WANG Keyou, LI Guojie. Review of real-time simulation of power electronic devices and power systems integrated with power electronic devices [J]. Automation of Electric Power Systems, 2022, 46(10): 3-17.

- [8] 高晨祥.电力电子变压器电磁暂态等效建模及实时仿真方法研究[D].北京:华北电力大学,2022. GAO Chenxiang. Research on the electromagnetic transient equivalent modeling methods and real-time simulation of power electronic transformer[D]. Beijing: North China Electric Power University, 2022.

- [9] CHALANGAR H, OULD-BACHIR T, SHESHYEKANI K, et al. A direct mapped method for accurate modeling and realtime simulation of high switching frequency resonant converters [J]. IEEE Transactions on Industrial Electronics, 2021, 68 (7): 6348-6357.

- [10] 许建中,高晨祥,丁江萍,等.高频隔离型电力电子变压器电磁 暂态加速仿真方法与展望[J].中国电机工程学报,2021,41 (10):3466-3479.

- XU Jianzhong, GAO Chenxiang, DING Jiangping, et al. Electromagnetic transient acceleration simulation methods and prospects of high-frequency isolated power electronic transformer [J]. Proceedings of the CSEE, 2021, 41(10): 3466-3479.

- [11] LI Z R, XU J, WANG K Y, et al. An FPGA-based hierarchical parallel real-time simulation method for cascaded solid-state transformer [J]. IEEE Transactions on Industrial

- Electronics, 2023, 70(4): 3847-3856.

- [12] GOLE AM, KERI A, NWANKPAC, et al. Guidelines for modeling power electronics in electric power engineering applications[J]. IEEE Power Engineering Review, 1997, 17

- [13] STEVIC M, SCHAUMBURG J, SCHLABERG T, et al. Challenges in real-time simulation of smart transformers [C]// 2022 IEEE 13th International Symposium on Power Electronics for Distributed Generation Systems (PEDG), June 26-29, 2022, Kiel, Germany.

- [14] CHEN W, RUAN X B, YAN H, et al. DC/DC conversion systems consisting of multiple converter modules: stability, control, and experimental verifications [J]. IEEE Transactions on Power Electronics, 2009, 24(6): 1463-1474.

- [15] PEJOVIC P. MAKSIMOVIC D. A method for fast timedomain simulation of networks with switches [J]. IEEE Transactions on Power Electronics, 1994, 9(4): 449-456.

- [16] 李珂, 顾伟, 柳伟, 等. 基于 FPGA 的变流器并行多速率电磁暂 态实时仿真方法[J]. 电力系统自动化, 2022, 46(13): 151-158. LI Ke, GU Wei, LIU Wei, et al. Real-time parallel multi-rate electromagnetic transient simulation method for converters based on field programmable gate array [J]. Automation of Electric Power Systems, 2022, 46(13): 151-158.

- [17] 王钦盛, 王灿, 潘学伟, 等. 基于 FPGA 的电力电子恒导纳开关 模型修正算法及实时仿真架构[J/OL]. 电力系统自动化:1-14 [2023-11-04]. http://kns. cnki. net/kcms/detail/32.1180. TP. 20231009.0854.008.html.

- WANG Qinsheng, WANG Can, PAN Xuewei, et al. Fixedadmittance switch model correction algorithm and real-time simulation architecture of power electronics based on field programmable gate array[J/OL]. Automation of Electric Power Systems: 1-14[2023-11-04]. http://kns.cnki.net/kcms/detail/ 32.1180.TP.20231009.0854.008.html.

- [18] 孙谦浩,宋强,王裕,等.基于RT-LAB的高频链直流变压器实 时仿真研究[J]. 电力系统保护与控制,2017,45(5):80-87. SUN Qianhao, SONG Qiang, WANG Yu, et al. Real-time simulation research of high frequency link DC solid state transform based on RT-LAB[J]. Power System Protection and Control, 2017, 45(5): 80-87.

- [19] WANG KY, XUJ, LIGJ, et al. A generalized associated discrete circuit model of power converters in real-time simulation [J]. IEEE Transactions on Power Electronics, 2019, 34(3): 2220-2233.

- [20] XU J, WANG K Y, WU P, et al. FPGA-based submicrosecond-level real-time simulation of solid-state transformer with a switching frequency of 50 kHz[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2021, 9(4): 4212-4224.

- [21] 徐晋.通用电力电子实时仿真方法研究及应用[D].上海:上海 交通大学,2019.

- XU Jin. Research and application of general power electronic real-time simulation methods [D]. Shanghai: Shanghai Jiao Tong University, 2019.

- [22] WATSON N R, ARRILLAGA J. Power systems electromagnetic transients simulation [M]. London, UK: Institution of Electrical Engineers, 2003.

- [23] ALLMELING J, RODRIGUEZ-DIAZ E, FELDERER N. Accurate real-time simulation of converters with frequent current commutation using sub-step events [C]// 2021 IEEE Vehicle Power and Propulsion Conference (VPPC), October 25-28, 2021, Gijon, Spain.

- [24] DONG ZR, GREGOIRE LA, VIPIN VN, et al. Real-time implementation of a dual-active-bridge based multi-level photovoltaic converter [C]// 2021 IEEE 12th International Symposium on Power Electronics for Distributed Generation Systems (PEDG), June 28-July 1, 2021, Chicago, USA.

- [25] 高晨祥,丁江萍,冯谟可,等.基于节点导纳方程预处理的ISOP 型 DAB 变换器双端口解耦等效模型[J]. 中国电机工程学报, 2021,41(6):2255-2267.

- GAO Chenxiang, DING Jiangping, FENG Moke, et al. Twoport decoupling equivalent model of ISOP type DAB converter by preprocessing the node admittance equation [J]. Proceedings of the CSEE, 2021, 41(6): 2255-2267.

- [26] 陈璐瑶. 基于 MMC 的电力电子配电变压器仿真研究[D]. 南 京:东南大学,2016. CHEN Luyao. Simulation research on MMC based power electronic distribution transformer [D]. Nanjing: Southeast University, 2016.

- [27] 高晨祥,王晓婷,丁江萍,等.基于电流过零点预计算的单有源 桥变换器等效建模方法[J].中国电机工程学报,2021,41(7): 2463-2474.

- GAO Chenxiang, WANG Xiaoting, DING Jiangping, et al. Equivalent modelling method of single active bridge converter by pre-calculating the current zero-crossing [J]. Proceedings of the CSEE, 2021, 41(7): 2463-2474.

- [28] 冯谟可,王傲群,袁帅,等.国产化电磁暂态仿真平台发展方向 分析及展望[J]. 电力系统自动化, 2022, 46(10): 64-74. FENG Moke, WANG Aogun, YUAN Shuai, et al. Analysis and prospect of development of China's independent electromagnetic transient simulation platform [J]. Automation of Electric Power Systems, 2022, 46(10): 64-74.

高晨祥(1997--),男,博士研究生,主要研究方向:电力电 子变压器电磁暂态等效建模。E-mail:chenxianggao@ncepu. edu.cn

林丹颖(2000-),女,硕士研究生,主要研究方向:电力电 子变压器离线并行仿真建模。E-mail:dylin702@163.com

韩林洁(1996--),女,博士研究生,主要研究方向:模块化 多电平换流器仿真、建模与控制。E-mail: linjie han@163.

冯谟可(1996-),男,通信作者,博士研究生,主要研究 方向:高压直流输电模块化多电平换流器电磁暂态建模。 E-mail: fengmoke1996@163.com

> (编辑 蔡静雯)

# Electromagnetic Transient Real-time Low-consumption Equivalent Model of Dual Active Bridge Based Power Electronic Transformer

GAO Chenxiang<sup>1</sup>, LIN Danying<sup>1</sup>, HAN Linjie<sup>2</sup>, FENG Moke<sup>1</sup>, XU Jianzhong<sup>1</sup>, LI Binbin<sup>2</sup>

(1. State Key Laboratory of Alternate Electrical Power System with Renewable Energy Sources

(North China Electric Power University), Beijing 102206, China;

2. Department of Electrical Engineering and Automation, Harbin Institute of Technology, Harbin 150001, China)

**Abstract:** Power electronic transformers (PETs) are key devices for power conversion in flexible DC distribution networks. Due to the limitation of simulation resources, the scales of existing electromagnetic transient (EMT) real-time simulations for PETs are small, which can not meet the demand of hardware-in-loop test and fast simulation for the large-capacity system. This paper proposes a real-time low-consumption equivalent modeling algorithm for dual active bridge (DAB) based PETs. Firstly, the binary input admittance characteristics of the high-frequency link port decoupling model (HFL-PDM) of the DAB are deeply explored and elaborated from the perspective of numerical analysis and physical significance. Based on this, the HFL-PDM of the PET with the N+1 characteristics is constructed. Secondly, a low-memory-occupancy EMT solution scheme using limited storage, a compact low-latency simulation framework, and a hardware implementation scheme using packet-based parallel pipeline computing are designed, which reduce the demand for the storage memory, the computing clock, and the hardware resource during the real-time simulation. Finally, the real-time low-consumption equivalent simulation model at a time step of 250 ns is developed based on Verilog language in RT-LAB. The simulation accuracy and resource utilization of the established model are tested.

This work is supported by Beijing Natural Science Foundation of China (No. 3222059).

**Key words:** electromagnetic transient real-time simulation; power electronic transformer (PET); dual active bridge (DAB); high-frequency link port decoupling; low resource consumption; RT-LAB